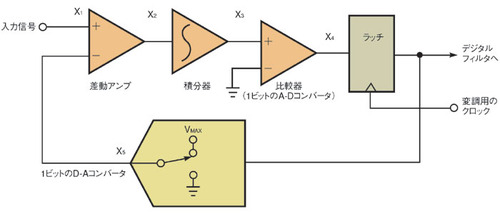

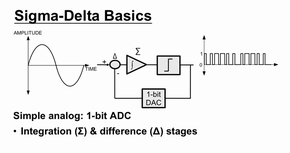

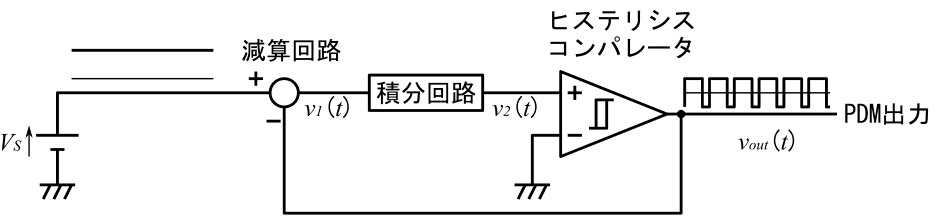

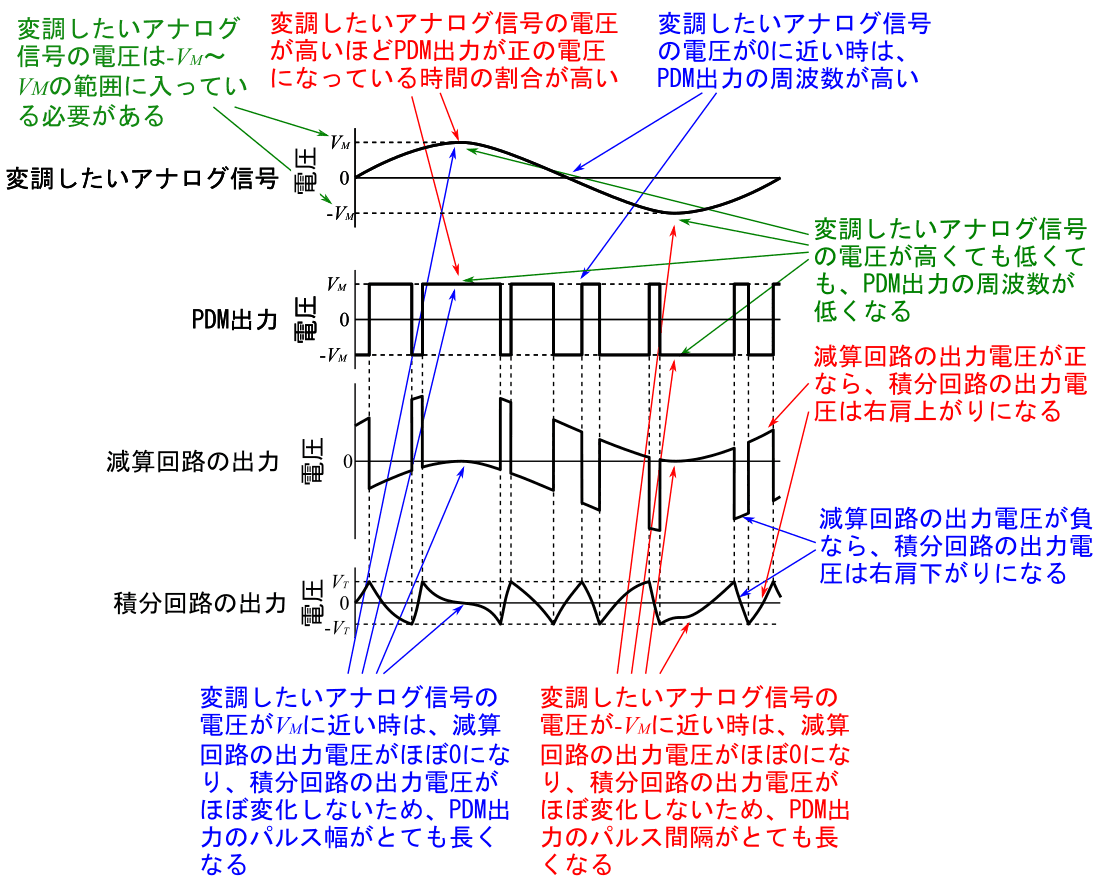

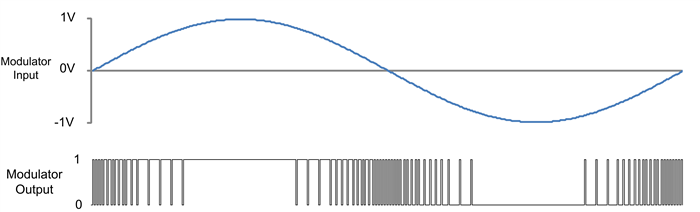

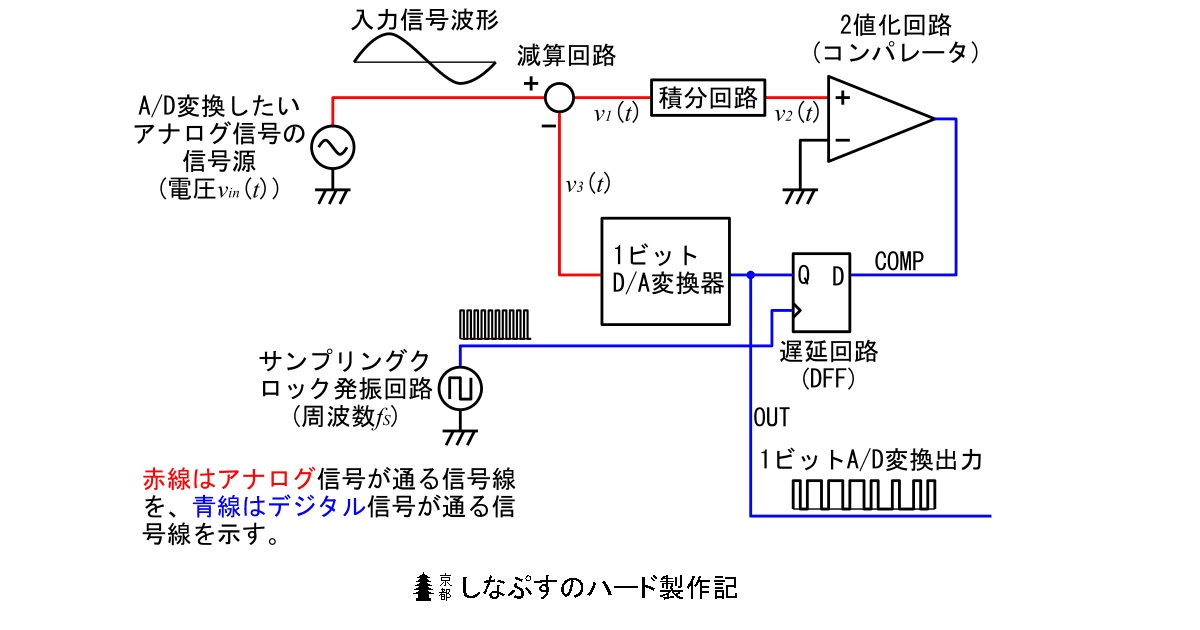

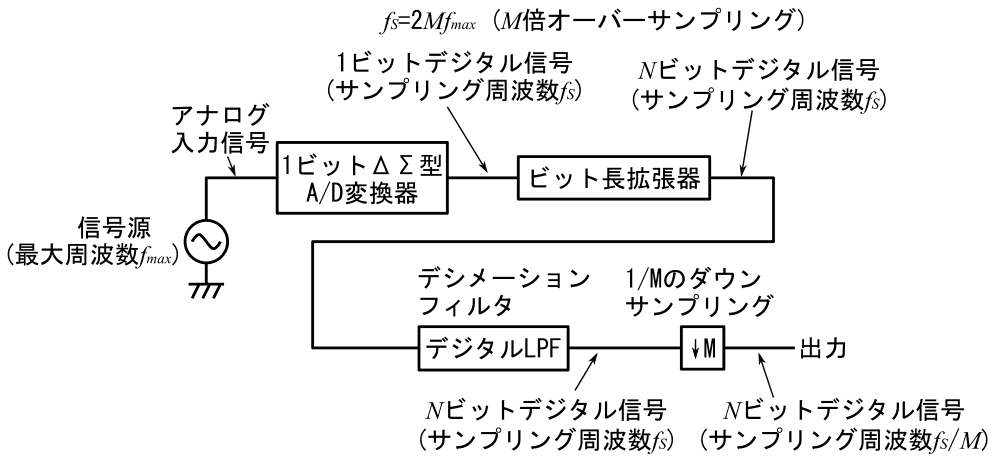

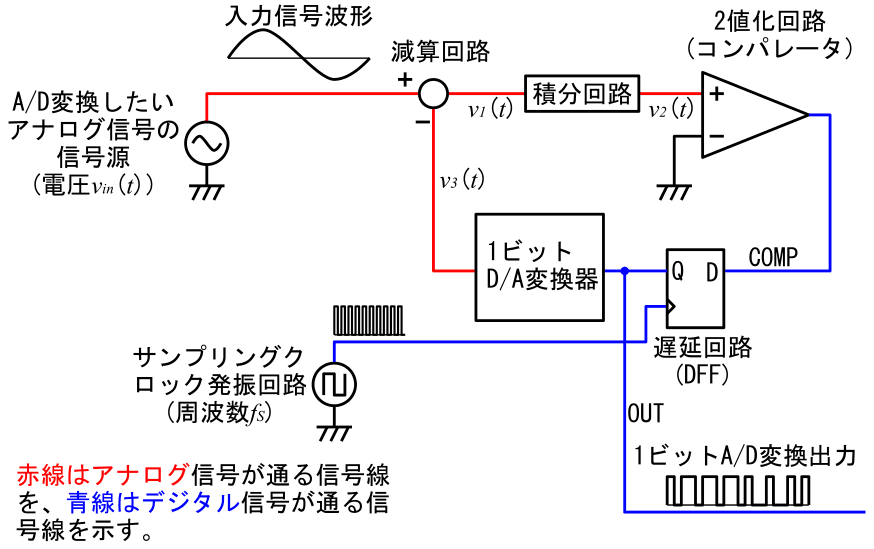

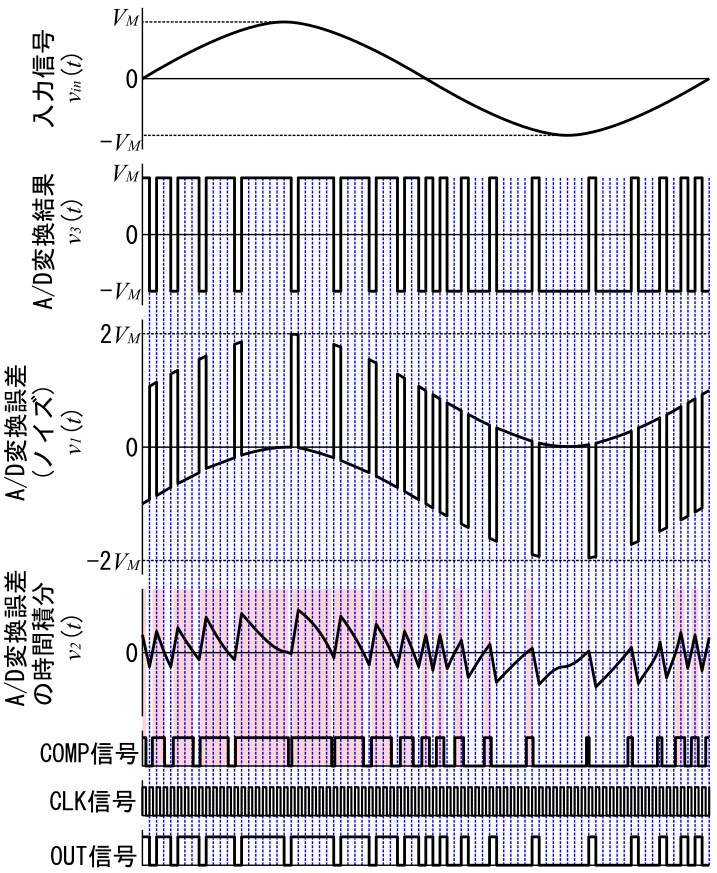

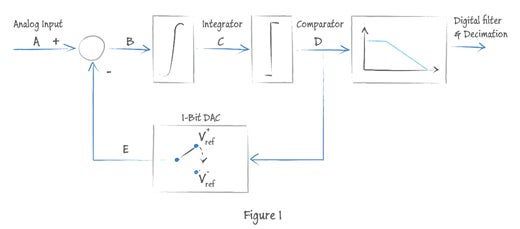

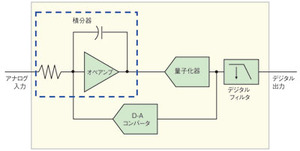

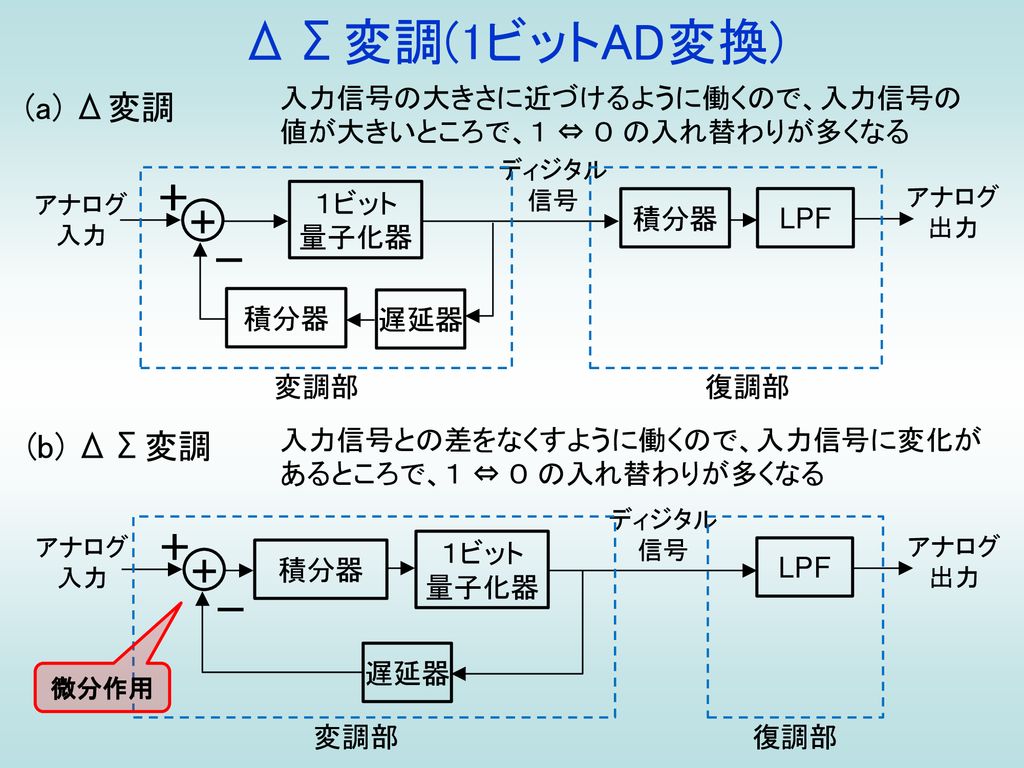

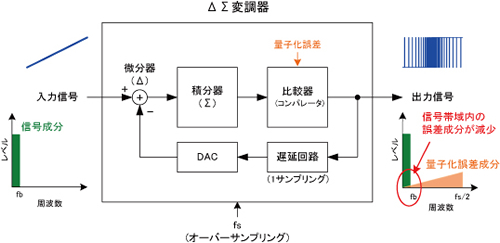

論を進める. 2 変調器 21 変調器の構造 変調器の基本構造である第3 図を用いて,アナロ グ信号からディジタル信号に変換する仕組みを説明する. 変調器は,ad変換器,da変換器,積分器,差分 器,遅延要素から構成されている.入力ノードにad変 換(量子 デルタシグマ変調の原理。 敗着は初手にあり。 信号のデジタル化には、サンプリングに際して必然的に発生してしまう不要な高い周波数を如何にして取り除くかという問題が、どれだけの 量子化 ビットが必要かという話も含めて常に付きまとう。 音声しかし、ΔΣ変調器のフィードバックループは非常に高い精度が必要であり、これがΔΣ方式の動作速度を制限してきました。 下の図に示すfm中間信号を用いるfmΔΣ変調器はこの問題点を解決できる可能性を秘めています。 まず、この方式の動作原理を説明

3 技術トレンド Internet Infrastructure Review Iir Vol 30 Iijの技術 インターネットイニシアティブ Iij

δσ変調 原理

δσ変調 原理- ΔΣ変調の原理と効能は AD 変換に於いては理解できるのですが 0101 の並びに過ぎないことから 0 か 1 かを判断できれば良い筈の Digital Audio 信号をΔΣ変調することは、どのような仕組みになっていてどのような効能があるのでしょうか? 積分器と量子化器と1ビットΔΣ変調器の最大SN比 10 50 100 500 4 6 8 10 12 14 16 18 22 24 50 100 150 オーバーサンプリング倍率 4次 3次 2次 積分器の次数=1次 S N 比 (d B ) 精 度 (b i t )

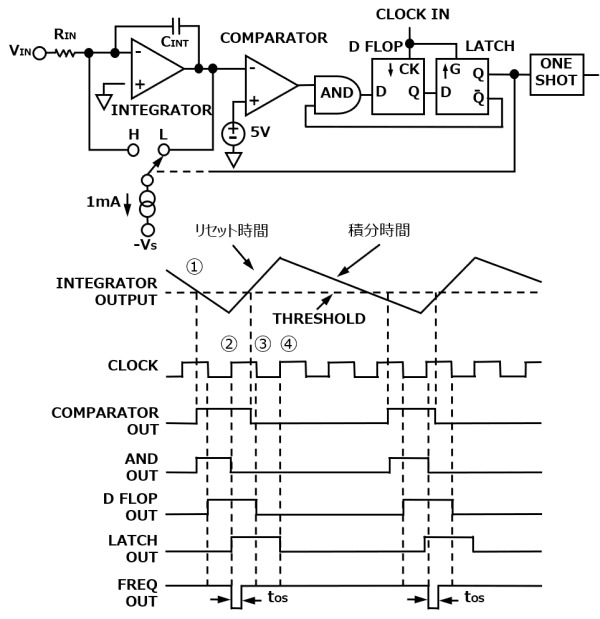

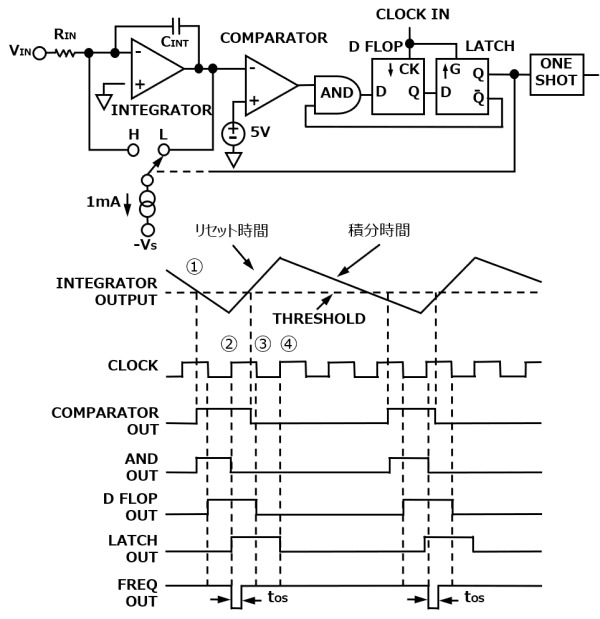

デジタルマルチメータの基礎と概要 Part2 第2回 技術情報 レポート Techeyesonline

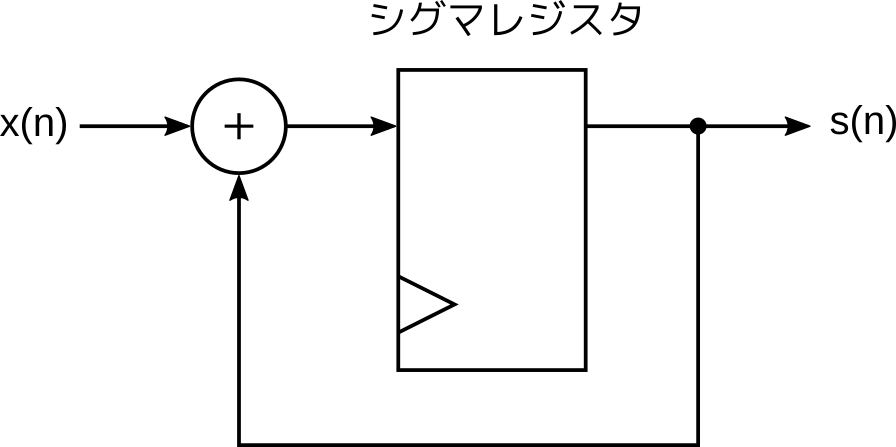

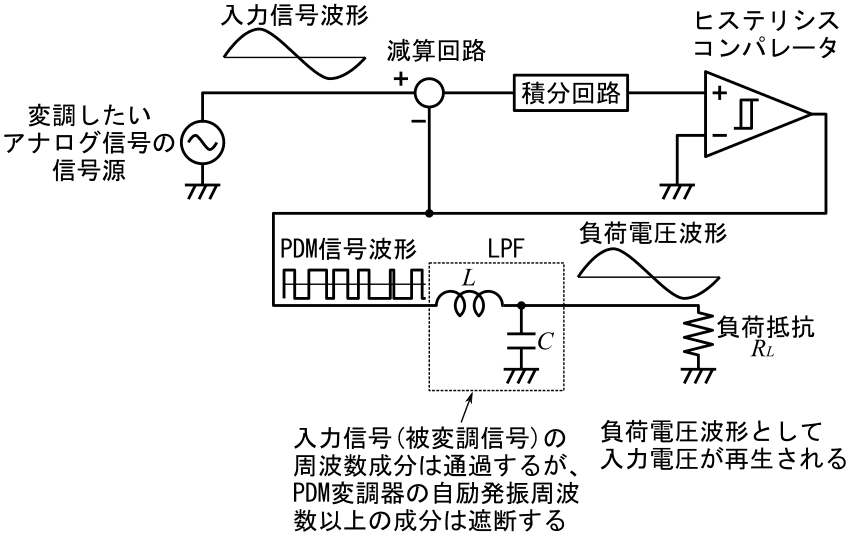

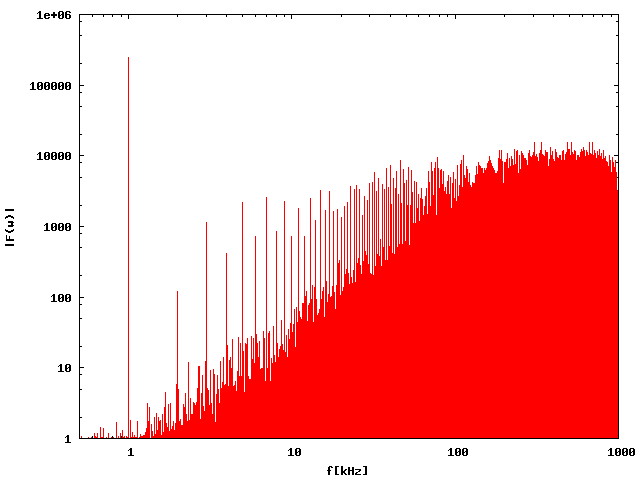

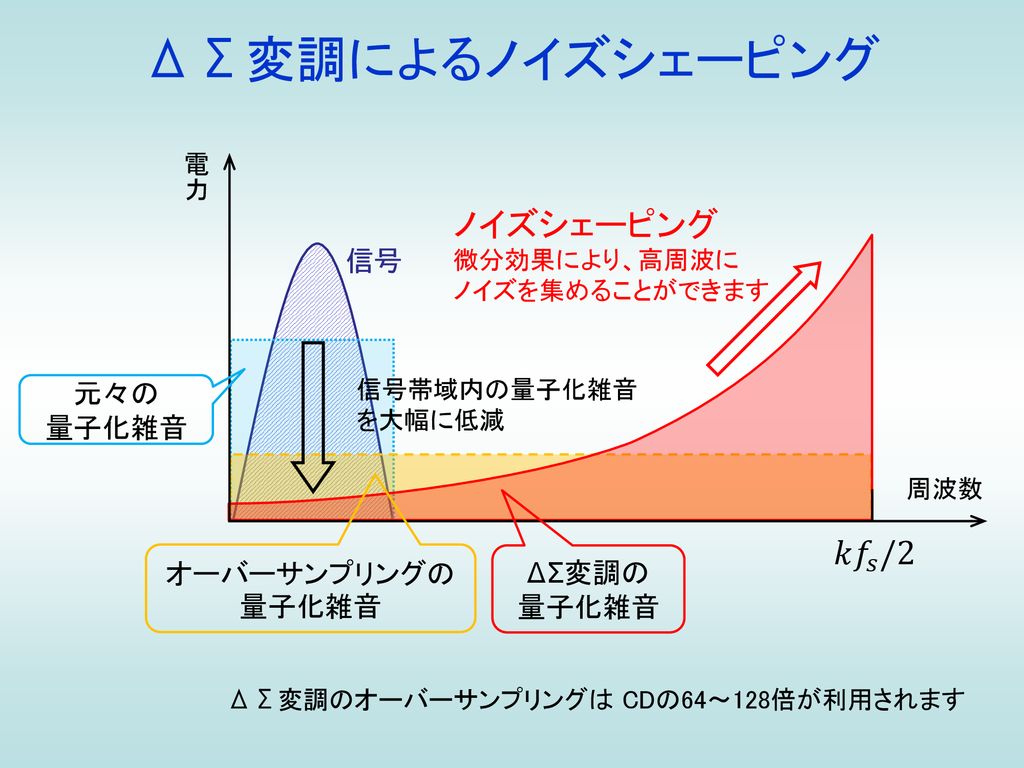

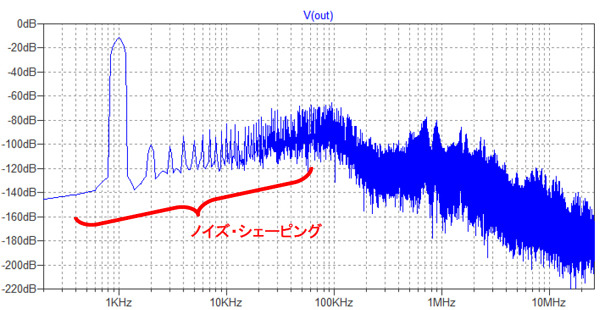

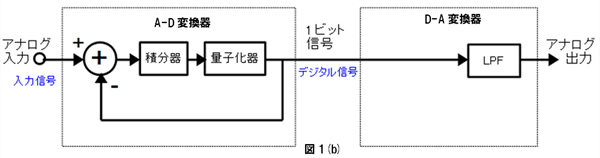

また、この回路はΔΣ変調を用いているため、入力信号に 1bit信号のような、PDMディジタル信号も扱うことができる。 3 シミュレーションによるPWM信号のスペクトル解析 ΔΣ変調は高次にすると、より低周波数領域での分解能が あがるという特性をもっている。シグマ・デルタ(ΣΔ)adc は、今日の信号アクイジションおよび処理システムの設計者が使用するツール・キットの中核となる要素です。本稿の目的は、ΣΔ adc トポロジーの基本原理に関する基礎知識を提供することにあります。adc サブシステムの設計に関係するノイズ、帯域幅、セトリング ノイズシェーパーの応用 ΔΣ型変調、DAC ノイズシェーパーの応用の代表的なものにΔΣ型変調器およびΔΣ型DAC(DAコンバーター)があります。 まず1次のΔΣ型変調器の例を示します。 まず入力された信号は前回の出力との差分を取り、その結果を積分し

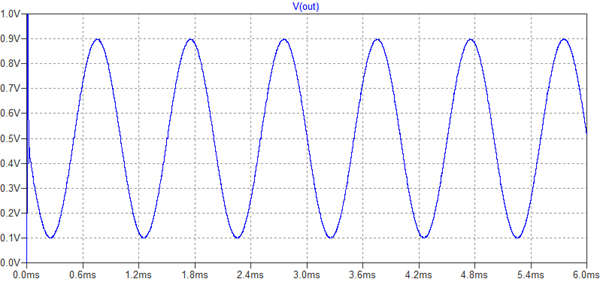

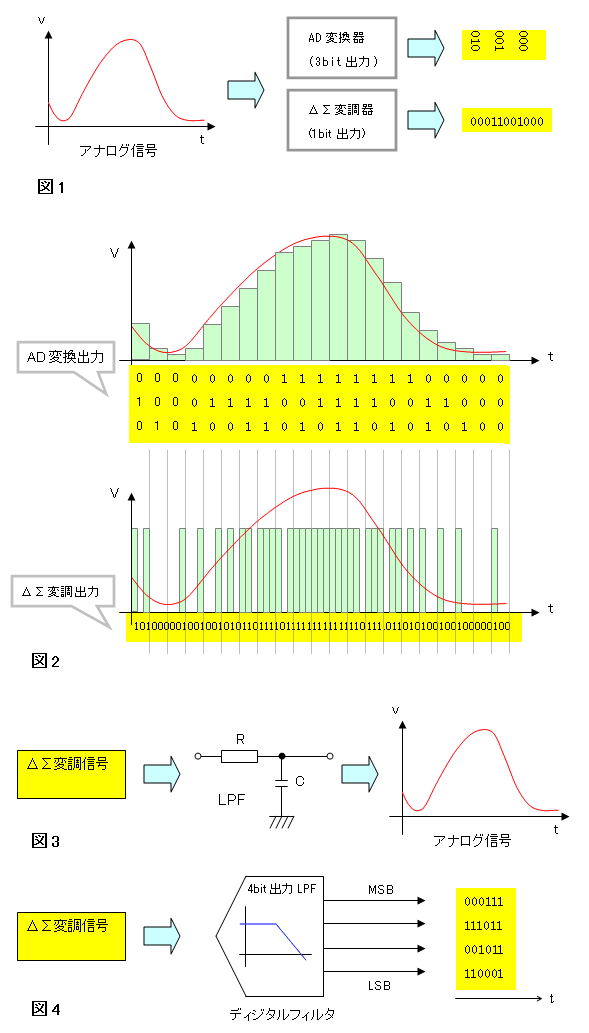

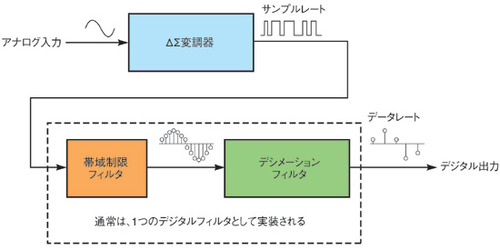

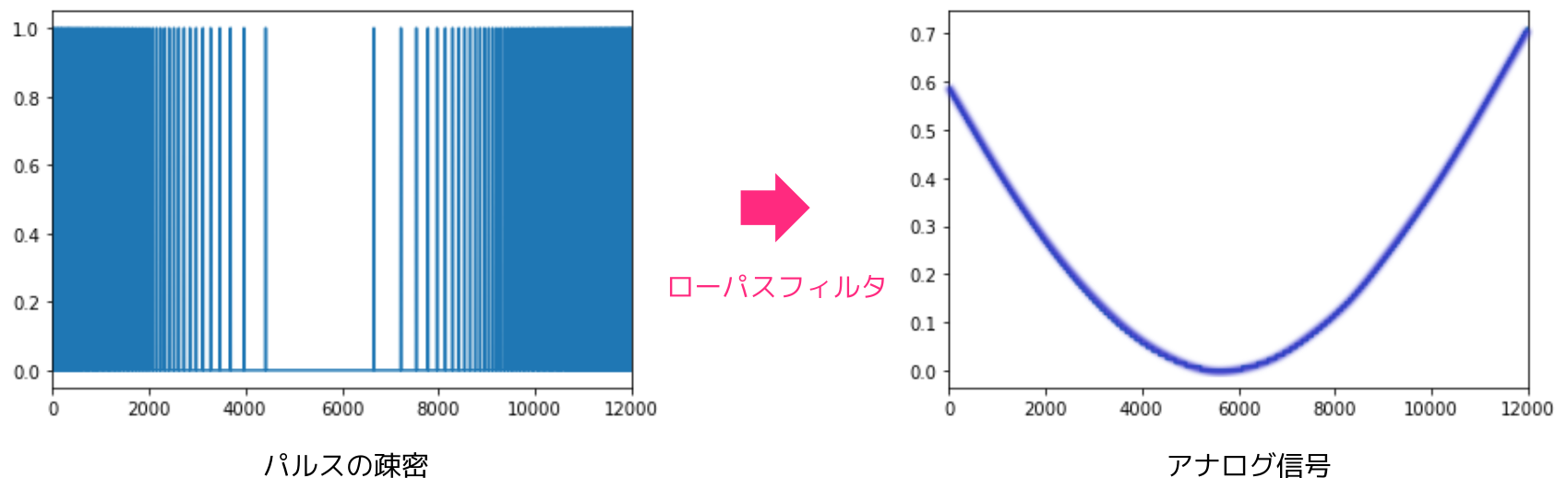

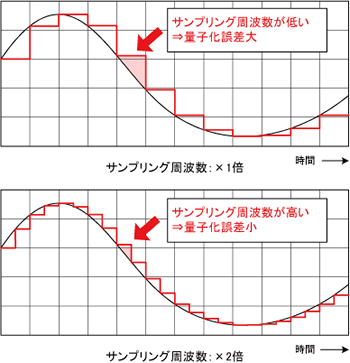

AD変換の基礎 / 第5回 デルタシグマAD変換器 連続的なアナログ信号から離散的なデジタルデータへの変換を請け負うADコンバーター(AnaloguetoDigital Converter)は、データ収集の中で非常に重要な役割を果たしています。 ADコンバーターの発展は長いのDAC が、 単一ビットDAC は原理的に直線性が保証さ 図2 ΔΣ変調器の出力パワースペクトル (振幅:1V, 正規化周波数:1/214 正弦波入力) Fig 2 Power spectrum of the ΔΣ modulator output amplitude 1, Input frequency 1/214) 〈22〉セグメント型DACの電流セルのミスマッチAdc 基本形4(ΔΣ型) adcΔΣ型 (デルタシグマ型) は、アナログ信号をオーバーサンプリングし、それをΔΣ変調を用いてアナログ信号の振幅に応じたパルス列に変換後、デジタルフィルタで帯域外のノイズ除去とデータの間引きを行うことで本来のサンプリング周波数でのデジタル信号への変換が

12 ΔΣ変調器の原理とノイズシェーピング ΔΣ変調器とは入力を,ノイズシェーピングされたスペクトルをもち,荒く量子化された出 力に変換するシステムである.その特徴からad 変換器等に用いられる.積分器と量子化器, どのように電波がデータを運んでいるのか知っていますか?今回は電波にデータを割り当てる変調について解説します。ask, fsk, psk, qamといった基本的な変調方式の原理と5g通信で使用されている256qamについても初心者にもわかりやすくまとめました。2 ΔΣ変調 〈2・1〉ΔΣ変調の特徴 ΔΣ変調は,アナログやマル チビット・ディジタルで表現されている信号を2値(1ビッ ト) の信号に変換する手法の一つである。ΔΣ変調の出力 は,たかだか1 ビット(1 と1 の2 値) であるが,オー

Ds型a Dコンバータのs N比 Baker S Best Edn Japan

2

1次ΔΣと呼ぶ DAC 積分器 量子化器 アナログ 入力 デジタル 出力 + - 遅延 回路 ∫ → 回路規模が 小さいことが特徴 必要な回路要素 ・積分器 ・ 量子化器(1bit) ・DAC(1bit) 実際の構成はΔΣ アナログ入力とデジタル出力DA変換して積分した信号との差分(Δ)を設計したΔΣ変調器ではosrを128とし,ΔΣ変調器 のサンプリング周波数は56mhzとする。次に,目標 のsnr及び発振限界を達成するためループフィルタ の次数を決める必要がある。osr=128と3次のルー プフィルタを用いたΔΣ変調器により110db以上のΔΣ(デルタシグマ)型adc を学ぶためのバイブル 丸善出版 新刊のご案内 ご注文・お問合せは・・・丸善出版(株)書籍営業部まで FAX03‐

平坂久門ただいま失業中 にわかavマニアの変換 サルでもわかる デルタシグマ変調 Ds方式dac 長文

第8回 連続時間方式のds型a D変換器 今 注目される理由 後編 日経クロステック Xtech

19年9月追記: この記事が度々PV上位に登場します.回路愛好者の皆様のご愛顧ありがとうございます! ちょっちD級アンプを作ろうかな~と思いつつ、アナログ信号→ビットストリーム変換をどうやっているのだろう?という疑問が生じ、調べました. まさかまさか、アナログ信号と図1に示すのは,ΔΣ型adcのブロック図です. ΔΣ型変換方式とはこのΔΣ変調回路のことでもあり ます.図1のΔΣ型変調回路の部分をもう少し詳しく 書いたものを図2に示します.この図が示すように, Δとは,比較器(以下,1ビットadcと呼ぶ)によっTitle dwm09_167_173_CMOS Created Date 8/6/03 926 PM

Ds変調 の解説 3 しなぷすのハード製作記

少し詳しいd 変調 ノイズシェーピング Electric

ウィキペディアにもΔΣ変調や1ビットに関する記述がある。 1bi Recorderを販売しているKORG 社にも解説ページがある。 1bitアンプを製造販売しているシャープのページにpdfで詳しい解説(論文)がある。 ウィキペディアにあるDSDの解説ページ。1bitAudioについて原理的にはたいへん簡単な変換法であり,レポート問題として考えて もらう予定. 容量アレイ型 これも簡単なので,レポート問題として考えてもらう予定である. パルス幅変調型 パルス幅変調(pulse width modulation, PWM) は,どちらかと言う ΔΣ変調の原理と効能は AD 変換に於いては理解できるのですが 0101 の並びに過ぎないことから 0 か 1 かを判断できれば良い筈の Digital Audio 信号をΔΣ変調することは、どのような仕組みになっていてどのような効能があるのでしょうか?

12 1650号 Ds変調器および信号処理システム Astamuse

2

変調方式 変調とはデータを伝送する際に最適な電気信号に変換することをいいます。 変調方式はアナログ変調、デジタル変調、パルス変調、スペクトラム拡散の4つに大きく分類されます。 ここでは、ロームの無線ラインアップで採用する変調方式の概要を説明します。以前(もうだいぶ前になりますが)FPGAにΔΣ型DACを実装できましたので、今度はADCを同様の原理で実装してみます。 シンプルな1次ΔΣ変調器で実験してみます。 モデルとしては下記の図のとおりとなります。 ∫で示したものが積分器、Qで示したのが量変調器は,アナログ回路特性がアナログディジタル変換特性に及ぼす影響が小さいこと は内部adc 出力を入力段に帰還することで,内部adc で生じる量子化雑音の低域成分を帰

Ds変調 の解説 1 しなぷすのハード製作記

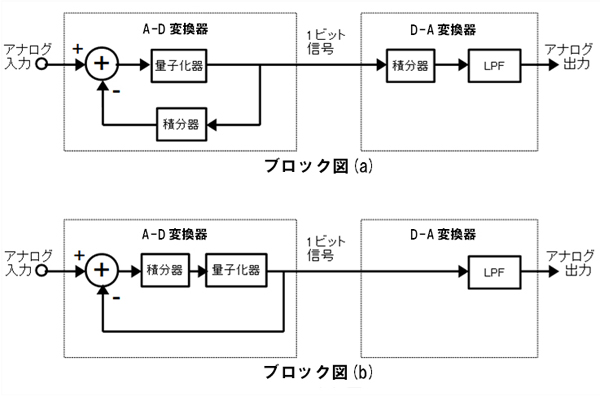

Ds変調を使用したa D D A変換回路はどっち Cq出版社 オンライン サポート サイト Cq Connect

Ak9223mk は内部ΔΣ変調を2次で行っているから、3次以上のsincフィルターを使用することが多いよ」 K先輩 「モーター電流検出では、この1bit出力ΔΣ型モジュレーターに絶縁機能を付加した『絶縁型ΔΣモジュレーター』が普及しているわ。

デルタシグマ変調の原理 敗着は初手にあり デジタルオーディオあれこれ

Ds変調を使用したa D D A変換回路はどっち Cq出版社 オンライン サポート サイト Cq Connect

デルタシグマ変調の原理 敗着は初手にあり デジタルオーディオあれこれ

2

2

Ds型a Dコンバータの要点 その2 Baker S Best Edn Japan

Ds変調とad変換 Electric

3 技術トレンド Internet Infrastructure Review Iir Vol 30 Iijの技術 インターネットイニシアティブ Iij

Ds型adコンバーター 東芝デバイス ストレージ株式会社 日本

Ds デルタ シグマ 型adコンバータ これだけは知っておきたいアナログ用語 Edn Japan

1

Ds型adコンバーター 東芝デバイス ストレージ株式会社 日本

一般社団法人 日本オーディオ協会 Dsd Direct Stream Digital

Ds型adコンバーター 東芝デバイス ストレージ株式会社 日本

Ds型a Dコンバータの要点 その1 Baker S Best Edn Japan

Ds型a Dコンバータの要点 その2 Baker S Best Edn Japan

デルタシグマ変調の原理 敗着は初手にあり デジタルオーディオあれこれ

Da コンバータがなくてもできる Fpga ピアノ 3 Acri Blog

Ds型adコンバーター 東芝デバイス ストレージ株式会社 日本

産業機器に向けた絶縁型ds変調器ic ルネサスが発売 日経クロステック Xtech

デルタシグマ変調の原理 敗着は初手にあり デジタルオーディオあれこれ

Ds変調 の解説 1 しなぷすのハード製作記

ノイズシェーピングの利用

Dsd ってほんとに良い音なの 1ビットって何 Gutsy Musik

Da コンバータがなくてもできる Fpga ピアノ 3 Acri Blog

アイドルトーンを除去するディザリング機能を含むds変調器およびディザリング方法

Ds型アナログ デジタル変換器入門 安田 彰 和保 孝夫 本 通販 Amazon

一般社団法人 日本オーディオ協会 Dsd Direct Stream Digital

Adc 基本形4 Ds型 A Dコンバータとは エレクトロニクス豆知識 ローム株式会社 Rohm Semiconductor

1997 5369号 2次デルタシグマ変調器 Astamuse

ノイズシェーパーの応用 Ds型変調 Dac 電子回路 マイコン Fpgaの設計引き受けます

Ds変調 の解説 1 しなぷすのハード製作記

Direct Stream Digital Wikipedia

Ds変調 Wikipedia

Da コンバータがなくてもできる Fpga ピアノ 3 Acri Blog

Ds変調を使用したa D D A変換回路はどっち Cq出版社 オンライン サポート サイト Cq Connect

Ds型adコンバーター 東芝デバイス ストレージ株式会社 日本

Delta Sigma Adc

デルタ シグマadcの基礎 デルタ シグマ変調器について アナログ Japan Ti E2e Support Forums

Ds変調 の解説 1 しなぷすのハード製作記

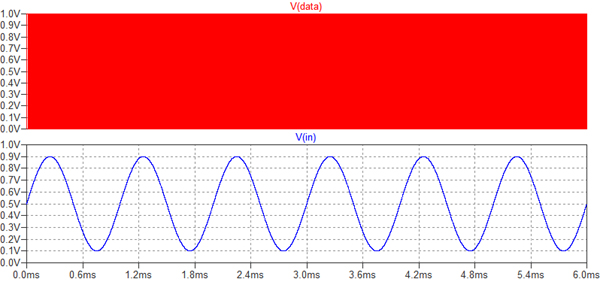

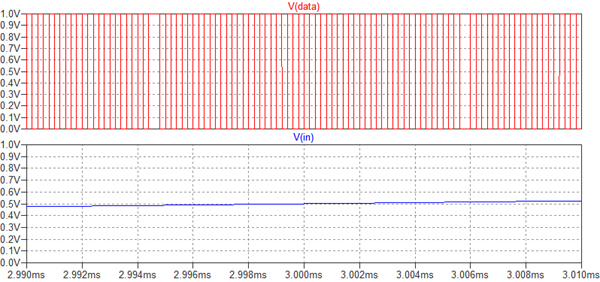

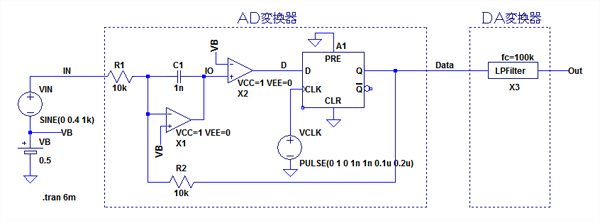

Dsーadc原理 その2 まだ解らん Lt Spiceを使ってsimulateしてみる

Dsーadc原理 その2 まだ解らん Lt Spiceを使ってsimulateしてみる

アナログ デジタル変換入門 原理と回路実装 コロナ社

がちさんの電子工房 Fpgaでds型adcの実験 その1 シミュレーション

2

Ds変調 の解説 1 しなぷすのハード製作記

Ds変調 の解説 3 しなぷすのハード製作記

Ds変調 の解説 2 しなぷすのハード製作記

プログラムでds変調器

2

01 号 アナログデジタル混在ds変調器 Astamuse

Delta Sigma Adc

Ds変調 の解説 3 しなぷすのハード製作記

Ad変換の基礎 第5回 デルタシグマad変換器 東陽テクニカ はかる 技術で未来を創る 機械制御 振動騒音

第13回 画像処理技術と音響処理技術 画像処理技術 空間周波数 Dct 静止画像圧縮 Jpeg 動画像圧縮 Mpeg Ppt Download

1997 5369号 2次デルタシグマ変調器 Astamuse

1997 5369号 2次デルタシグマ変調器 Astamuse

少し詳しいds変調 始めにd変調ありき Electric

デジタルマルチメータの基礎と概要 Part2 第2回 技術情報 レポート Techeyesonline

Ds型アナログ デジタル変換器入門 和保孝夫 Hmv Books Online

1997 5369号 2次デルタシグマ変調器 Astamuse

発見と発明のデジタル博物館 画像通信における信号処理技術 専門向け

Ds変調応用icの進化は止まらず アナログicベンダーが新製品を続々投入 1 2 ページ Edn Japan

量子化制御入門 動的量子化 Ds変調 制御理論 Youtube

Dsーadc原理 その2 まだ解らん Lt Spiceを使ってsimulateしてみる

少し詳しいds変調 序 Electric

デルタシグマ変調の原理 敗着は初手にあり デジタルオーディオあれこれ

第13回 画像処理技術と音響処理技術 画像処理技術 空間周波数 Dct 静止画像圧縮 Jpeg 動画像圧縮 Mpeg Ppt Download

Ds型adコンバーター 東芝デバイス ストレージ株式会社 日本

ブランドはミームと成れるか 6 Studer編

パルス密度変調 Wikipedia

Ds変調を使用したa D D A変換回路はどっち Cq出版社 オンライン サポート サイト Cq Connect

2

Ds変調を使用したa D D A変換回路はどっち Cq出版社 オンライン サポート サイト Cq Connect

Ds変調を使用したa D D A変換回路はどっち Cq出版社 オンライン サポート サイト Cq Connect

Electronic Diy With Arduino

デルタシグマ変調の原理 敗着は初手にあり デジタルオーディオあれこれ

04 号 Ds変調方式のa d変換器及びこれを用いた制御装置 Astamuse

アナログ デジタル変換回路 Wikipedia

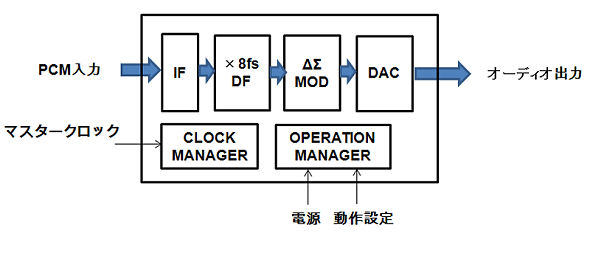

オーディオ機器の要 D Aコンバータic の機能と構成 デジタルオーディオの基礎から応用 4 2 4 ページ Edn Japan

Adc 基本形4 Ds型 A Dコンバータとは エレクトロニクス豆知識 ローム株式会社 Rohm Semiconductor

1997 5369号 2次デルタシグマ変調器 Astamuse

Ds変調

ブランドはミームと成れるか 6 Studer編

2

第1回 中 低速分野のa D変換は Ds型が今後の主流になる 日経クロステック Xtech

Ds変調を使用したa D D A変換回路はどっち Cq出版社 オンライン サポート サイト Cq Connect

高分解能a D変換器の基礎 Ds変調器の動作を理解する 日経クロステック Xtech

ノイズシェーパーの応用 Ds型変調 Dac 電子回路 マイコン Fpgaの設計引き受けます

シグマデルタ変調器 デルタシグマ変調 動的量子化器 Youtube

Ds型adコンバータ Adc のexcelによる動作シミュレーション さしあたって

0 件のコメント:

コメントを投稿